본 글은 학부생의 복습을 위해 정리한 글이며 제 글보다 전공책을 먼저 보는 것을 추천 드립니다. 틀린 내용이 있을 수 있으니 댓글 남겨주시면 감사하겠습니다.

1. Sheet Resistance 면 저항

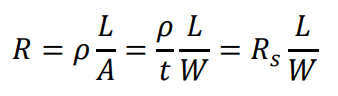

면 저항은 Rs로 표기하고, 단위 면적당 저항을 의미합니다. 다음과 같이 정의할 수 있습니다.

따라서 면저항 Rs = ρ/t가 되고 단위 면적당 저항이기 때문에 단위는 Ω/□ (ohm per square)가 됩니다.

저항의 측정 단위라고 생각하면 되고 반도체 소자의 dimension이 달라짐에 따라 R을 일일이 계산하기엔 불편하기에 L/W 비율(Square)을 남기고 Rs 값을 공유한다고 생각하시면 됩니다.

간단하게 생각하면 R = Rs * 정사각형 개수가 됩니다.

어떻게 면 저항을 측정할까요?

Four-point probe 방법이 있습니다.

이 방법은 동일 선상에 일정 간격으로 정렬한 4개의 probe로 시료 표면에 대어 전류와 전압을 가해 저항을 측정하는 방식입니다. 보정 계수를 적용하여 면 저항을 구합니다. 식은 다음과 같습니다.

측정이 간단하고 빠르게 데이터를 확보할 수 있다는 장점이 있습니다.

이외에도 Hall mesurement, Van der Pauw method 방법 등이 있습니다. 더 구글링하면 나와요

2. Contact Resistance 접촉 저항

접촉 저항은 접촉한 두 전도성 물질 사이 전기 흐름에 대한 저항입니다.

우리에게 익숙한 MOSFET을 보면 이해하기 쉬운데요

MOSFET에서 Source에서 Drain으로 전자가 이동하면서 느끼는 저항으로 Rc, Rch가 존재하게 됩니다.

(물론 다른 자잘한 저항도 존재합니다. 여기선 매우 작다고 보고 고려하지 않겠습니다.)

따라서 최종적인 저항은 다음과 같습니다.

R_total = R_channel + 2 * R_contact

이때 Gate에 걸리는 전압을 조절하여 Rch는 controllable하지만 Rc는 controll이 어렵습니다.

그래서 우리는 Rc를 낮추기 위해 노력해야 합니다. 여러 방법이 있겠죠? 공정 최적화나 MS contact을 조절하는 뭐 그런 ,,,

Rc는 어떻게 측정할 수 있을까요?

TLM(Transmisson Line Mesurement) 방법을 사용합니다. 이 방법은 여러 개의 금속 패드를 일정한 간격으로 형성한 후 두 패드 간의 저항을 측정하는 방법입니다.

간격을 x1, x2, x3로 늘리면서 측정되는 총 저항 또한 간격과 linear하게 늘어나게 됩니다.

3. Capactitance, Capacitor, Cap

귀찮으니 캡이라고 부르겠습니다. 캡은 전하가 전압에 의해 저장되는 능력을 의미하고 다음과 같이 씁니다.

C = Q/V or Q = CV

정의대로 식을 쓰면 C = k*ϵ_0*A/d 이고 k는 유전 상수, ϵox는 진공에서의 유전 상수를 말합니다.

반도체 소자에서는 MOS 구조에서 산화막이 중요한 역할을 한다는 것을 배우셨을 겁니다.

C = Cox * A 라고 정의하면 산화막의 캡은 다음과 같습니다.

Cox = k*ϵox/tox [F/m^2]

기존에 사용하는 SiO2의 유전율(K)은 3.9이고 이보다 더 높은 물질을 High-K, 낮은 물질을 Low-k라고 합니다.

유전율이 높으면 전자가 잘 움직이는 것이고 낮으면 잘 움직이지 않아서 절연이 잘 된다고 생각하시면 됩니다.

반도체 소자에 빠르게 켜지고 꺼지면 좋으니까 Oxide 자리에 high-k 물질을 사용하면 전력 소모도 줄고 속도도 빨라지겠죠? 그러나 Trade-off를 생각해야 합니다. 전자가 잘 움직이다보니 누설 전류도 더 잘 발생하게 된다는 단점이 존재합니다.

산화막이 얇더라도 높은 캡을 유지하면서 leakage를 줄이는 것이 목표인 high-k 물질은 주로 MOSFET, DRAM, FinFET, GAAFET 의 Oxide 절연체로 활용되고 있습니다. Low-k 물질은 전력 반도체에 주로 사용되고 있습니다.

4. CV curve

Q = CV인 것 기억하시죠? C-V curve에 대해 알아봅시다.

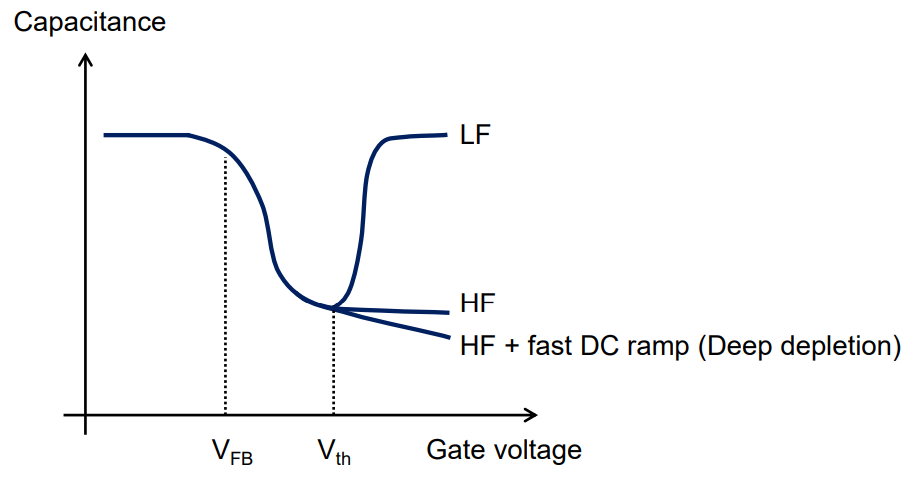

MOS 구조에서 Accumulation -> Depletion -> Inversion에 따라 Cap이 바뀌는 것을 위 그래프로 확인할 수 있습니다. 그러나 주파수에 따라 그래프가 달라질 수 있습니다.

LF(저주파)에서는 Depletion 영역에서 캐리어가 충분히 반응할 수 있어 cap의 영향이 크지 않지만 HF(고주파)에서는 얘기가 다릅니다. 캐리어가 게이트 전압 변화에 즉각적으로 반응하지 못해 inversion이 일어나지 않아서 정전 용량이 위 그래프처럼 올라가지 않고 오른쪽에 검정 그래프처럼 일정한 최소값을 유지하게 됩니다.

전자회로에서 Bypass cap이나 Decoupling cap을 공부하게 될 때 이 내용이 떠오를 겁니다!!

정리하면 다음과 같습니다.

| 영역 | 저주파 | 고주파 |

| Accumulation | Ci | Ci |

| Depletion | Cap 감소 | Cap 감소 |

| Inversion | 증가 | Cmin 유지 |

주파수 말고도 CV curve에 영향을 주는 요인으로 Qf, Qm, Qit, Qt 등이 존재하는데 이 중 두 개에 대해 알아봅시다. Oxide Charge와 Interface Trap이 있습니다.

Qf는 fixed Oxide Charge를 의미하고 SiO2 내부에 위치한 전하들입니다. 이미 공정 과정에서 박혀있어서 일반적으로 불변합니다. 이는 Vt의 변화를 유도하기 때문에 엔지니어 입장에선 좋은 일이 아닙니다 ㅠㅠ

interface trap은 Dangling Bond나 계면의 오염 등 결함으로 인해 Si/SiO2 계면에 전하가 trap된 것으로 소자의 일관된 동작(Vt 되었을 때 딱 켜지고 꺼지는)을 방해합니다. 이로 인해 위 오른쪽 그래프처럼 Slop이 눕게 되는 것입니다. 눕는다는 건 딱 켜지고 꺼지는 상태가 아니란 것을 의미하죠!

cf) Dangling bond 댕글링 본드는 표면에 결합하지 못한 채 남은 전자를 의미합니다. 결합을 못했으니 불안정하고 불안정하니까 캐리어가 달라붙겠죠? 그래서 이를 해결하기 위해 Forming Gas 어닐링 등을 해준답니다.

감사합니다.

'전공 > 반도체소자' 카테고리의 다른 글

| [반도체소자] MOSFET (0) | 2025.02.17 |

|---|